みなさんこんにちは。今回は私も参加したIC製造プロジェクト”TinyTapeout”について紹介したいと思います。

TinyTapeoutとは

TinyTapeoutは、参加者が作成・投稿したICの設計データをもとに、実際にICを製造するという教育目的のプロジェクトです。

有志による設計データを募り、ICを製造する試みはTinyTapeout以前にも金沢大学の秋田先生を中心としたMakeLSI:や、Google/efablessによるOpenMPWなどがありますが、TinyTapeoutはこれらのプロジェクトよりも参加するためのハードルが低くなっているのが特徴です。

MakeLSI:はトランジスタおよびそれらの間の配線の物理的なレイアウトをそのまま描くことでICの設計を行う必要があります。また、OpenMPWは抽選制なので必ず作ってもらえる保証がなかったり、自前で環境構築をして1物理レイアウトデータを生成する必要があります。

一方、TinyTapeoutではOpenMPWでも使用できるVerilog HDL以外にも、WokwiというGUIベースの回路シミュレーターを使ってICを設計することができます。さらに、TinyTapeoutではVerilog HDL/Wokwiのプロジェクトのデータから物理レイアウトデータを生成するための一連のワークフローがGitHub Actionsで提供されています。これによって、手元に論理合成や配置配線をする環境を構築せずにICの設計データを作ることができます。

TinyTapeoutは使用する製造プロセス自体はOpenMPWと同じですが、efabless/Googleのスポンサードによる無償プログラムであるOpenMPWとは異なり、efabless社のchipIgniteという有償サービスを使っています。chipIgniteは一般にはMPW(Multi Project Wafer)またはシャトルと呼ばれる、1枚のシリコンウエハに複数のICの設計を相乗りさせて製造するサービスです。

ICの回路規模やウエハのサイズによりますが、1枚のウエハからは数百~数千個のICが得られるため、検証用などで必要数が少なければ相乗りさせても十分な数のICが得られます。一方でウエハを製造するコストは相乗りする設計間で分担できますから、シャトルサービスはコストを抑えてICを試作する手法として活用されています。efabless/chipIgniteはシャトルサービスの中でも、従来は商用ツールとNDAで守られたPDK(Process Design Kit:物理レイアウト用の設計データ)が必要だったところを、オープンソースのツールとオープンなPDKでICを製造するところまでできるようにしているのが特徴です。

さて、話を元に戻すとchipIgniteは低コストを実現できるシャトルサービスではあるものの、元々の半導体製造サービスの価格が価格なので1設計(1区画)あたり約1万ドルというお値段となります。そこで、TinyTapeoutではchipIgniteの1区画をさらに細かく分割し、細分化された1区画を50ドルで販売しています。

実際のIC(評価ボードに実装済)は別途100ドルで購入となり、日本からだと送料が追加で10ドルかかるので、自分の設計したICを製造してもらい手に入れようとすると最低160ドルかかることになります。2024年2月現在の為替レートだと約2.4万円となり、ちょっと高い気もしますが、自分で設計したICを手に入れるというロマンのために出せなくもない金額と言えると思います。

今までのところTinyTapeoutは5回の設計データ募集/製造を実施しています。私も第5回の製造に設計データを投稿しました。私は学生時代にFPGAを使ったリコンフィギャラブルシステムの研究をテーマにしていたので、Verilog HDLは書けるし、TinyTapeoutならそのあとのツールチェーン環境構築の手間もほぼ無いので、これなら休みの日を使ってちまちま進めるのでもなんとかなりそうだ!と思いトライすることにしたのでした。

ちなみに、これまでの5回の募集のうち、第3回までと第4回以降で細分化されたそれぞれの区画をつなぐ回路の構成が変わっています。これにより第4回以降は動作周波数が最大で12.5kHz程度と大変遅いという第3回のTinyTapeoutまでに存在した課題が解決され、最大50MHz程度で動くようになっています。この制約が外れたことで、結構遊べる回路が実装できるようになったのではないかと思います。

なお、TinyTapeoutは現在6回目の製造用の設計データを募集しているところです。しかし日本語でTinyTapeoutに言及しているWebサイトは第4回に参加されたISHI会の今村さんのハンズオン資料、私と同じく第5回に参加したkeropiyo3さんの「Tiny Tapeoutで半導体チップ設計に挑戦した話」など、かなり少ないようです(その他、私がTinyTapeoutを知ったきっかけになった秋田先生のPostなど、X上では多少言及があるようです)。そんなわけで、日本からのTinyTapeout参加者と日本語のTinyTapeout情報を増やすべく、今回紹介記事を書いてみました。

TinyTapeout05に参加してみた

先ほども書いたように、私は前回(第5回)の募集であるTinyTapeout05に参加しました。TinyTapeoutの概要とWokwiを使った設計の手順は前述の今村さんのハンズオン資料が大変詳細に書かれているので、ここでは自分がどんなICを設計を中心に書いておきたいと思います。

TinyTapeout05は2023年11月に募集が締め切られたのですが、実際のウエハに回路を焼き付けて製造しているためにそんなにすぐ実際のICが届くわけではありません。ICと評価ボードが手元に届くのは今年の5月になるようです。ちょうど最近、2022年12月締め切りだったTinyTapeout02(第2回)のICが参加者の手元に届き始めたようです。私のICも届いたら実際に動作確認を行ってまた記事を書きたいと思います。

今回作ったもの

今回TinyTapeoutに応募するにあたり設計したのは波形メモリ音源ICです。いきなりCPUとかを書いてもよかったのですが、1区画が小さいので頑張って書いたCPUがいざレイアウトしてみたら入りませんでした!となっても嫌だなぁということと、せっかくなら作った後も遊べるものをということで音源ICを作ることにしました。

最初はいわゆる矩形波オンリーのPSG風音源だけのつもりだったのですが、結構面積的に余裕があったことと、PSG風音源だけだとマイコンでも簡単に再現できてしまうの2で、ゲームボーイの音源の仕様を参考にしながら波形メモリ音源を追加しました。結局波形メモリ音源用のメモリを追加したら微妙に1区画に入りきらず50ドル追加してもう1区画買い足すという本末転倒な話もあったりします…

ちなみにTinyTapeoutでは上に書いたように区画を追加購入して、1つの設計で2個以上の区画を使うこともできます。現在のところ、最大で8×2=16区画を1つの設計で使うことができるようです。

なお、私が作成した設計データはGitHubに”tt05-TYE-tone-generator“として置いてあります。Verilog HDLの範囲で収まるように組み合わせ回路はfunctionで書いたりしていますが、後で試したらalways_combなど、SystemVerilogの構文も使えるようでした。

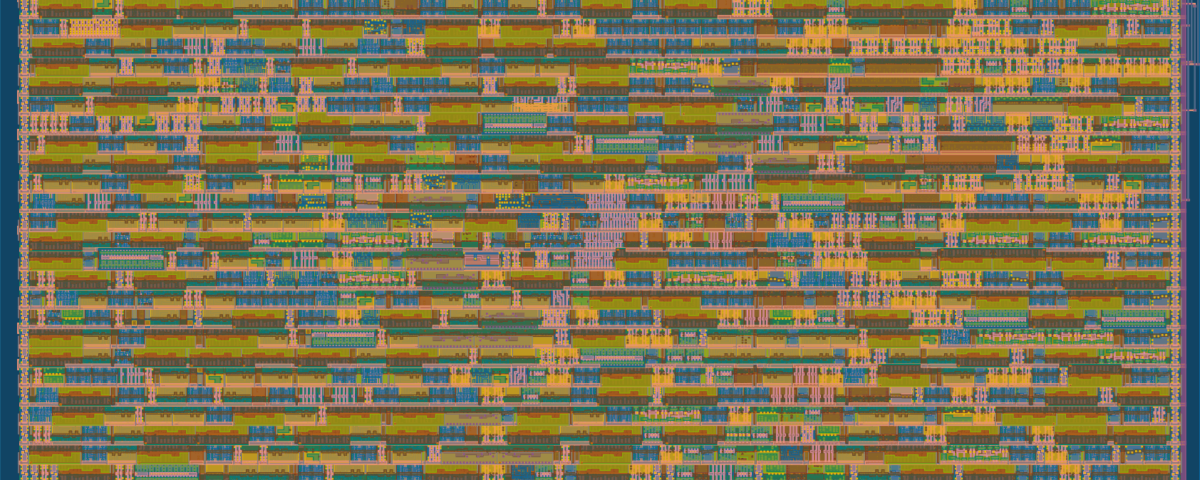

GitHub上で物理レイアウトデータの生成が終わると、セットでICの内部構造の3Dモデルも生成されて、こんな感じでグリグリ回して眺めることができます。

仕様

今回作成した波形メモリ音源ICの仕様は以下の通りです。

- 同時4和音発音可能

- 発音波形は各チャンネルごとに以下から選択可能

- 矩形波

- Duty比12.5%

- Duty比25%

- Duty比50%

- 波形メモリ

- 4-bit x 32wordの波形

- 4-bit x 16wordの波形(32wordの前半/後半2種から選択)

- 4-bit x 32wordをシャッフルした波形

- ホワイトノイズ

- 矩形波

- 音量は矩形波/ホワイトノイズは256段階、波形メモリは8段階設定

- SPIで外部から制御

- 出力はI2S 16bitモノラル

結局2区画使ってしまいましたが、いわゆるPSG音源ICは矩形波が3チャンネルなので、それより1チャンネル多くできましたし、波形メモリ音源にも対応できたのでいろいろ遊べると思います。一方でハードウェアエンベロープは省略してしまったので、発音中の音量変化を実現するには外部から制御してやる必要があります。

工夫したポイント

いくつかこだわった(手を抜いた?)ポイントがあるので、それも書いておこうと思います。

過去の設計の流用

SPIの受信回路およびI2Sの送信回路は「ESP32+FPGAオーディオ基板でPCM音源を作る(1)」などで紹介しているFPGA向けに作ったVerilog HDLのソースを今回の用途に合わせて修正して使いました。

ピン配置

第4回以降のTinyTapeout向けの評価ボードにはRP2040マイコンが搭載され、製造したICのテストに使えるようになる予定になっているので、RP2040のSPIが製造したICのSPIにつながるようなピン配置として設計しました。

回路規模の節約

TinyTapeout05の1区画は約160um x 100umで、公式FAQによるとだいたい1区画に入れられるのは1000ゲート程度とのことでした。ここにできるだけ機能を詰め込むべく、以下のような設計としました。

- 4チャンネル分の処理は1つの処理ブロックを時分割で共有して実施

- 1チャンネル分の処理もさらに時分割して1つの16bit加算器を使いまわして実施

- 2の補数の代わりに1の補数で負数を代用

- 同じようなタイミング信号を作るためのカウンタはモジュール間で共有

とにかく使える面積が小さいので、処理を時間方向に分散させて、それぞれの時間で使えるリソースは使いまわしたり、出音への影響が少ない範囲で回路を簡単化するような工夫をしました。d.に関してはちょっとやりすぎて、終盤にファンアウト(ある回路の出力先の個数)が多すぎるという旨のエラーが出たりしました。回路規模とのバランスや設計のメンテナンス性も含めて、全体を見ながら考える必要がありそうです。

FPGAでの動作確認

もちろんVerilog HDLで書いているのでシミュレーションもやるのですが、音源ICだし実際に音を出して確認したいと思い、「ESP32+FPGAオーディオ基板でPCM音源を作る(1)」で使ったESP32+FPGAオーディオ基板のFPGAに今回の設計を実装して動作確認を行いました。リアルタイムの動作で検証できるのは便利なのもそうですが、実際に音が出る環境を用意しながら設計を進めるのはモチベーションの維持にもよかったのではないかと思います。

TinyTapeout06は現在募集期間中!

というわけで今回はオレオレICを作ることができるプロジェクト、TinyTapeoutについて紹介しました。先ほども書いたようにTinyTapeoutでは現在第6回の製造に向けた設計データを募集しています。なお、第5回までは原則としてデジタル回路のみの受付ですが、第6回はアナログ回路も混在させた設計も受け付けるようです。締め切りは2024年4月19日なのでまだまだ十分時間はあります。みなさんもぜひ、自分の設計した回路をICにしてみませんか?