アーキテクチャについて

1.概要

- シンプルなRISC指向 CPU

- 命令長、レジスタ長ともに16bit(16bit=2byte=1word)

- ワードマシン(16bitごとにメモリアクセス)

- 16本のレジスタ

- ノイマン型を採用(非ハーバードアーキテクチャ)

- Spartan-3E XC3S250Eにおいて60MHz動作可能

- 1命令サイクル=3クロック(=20MIPS@60MHz)

2.CPUの内部構成

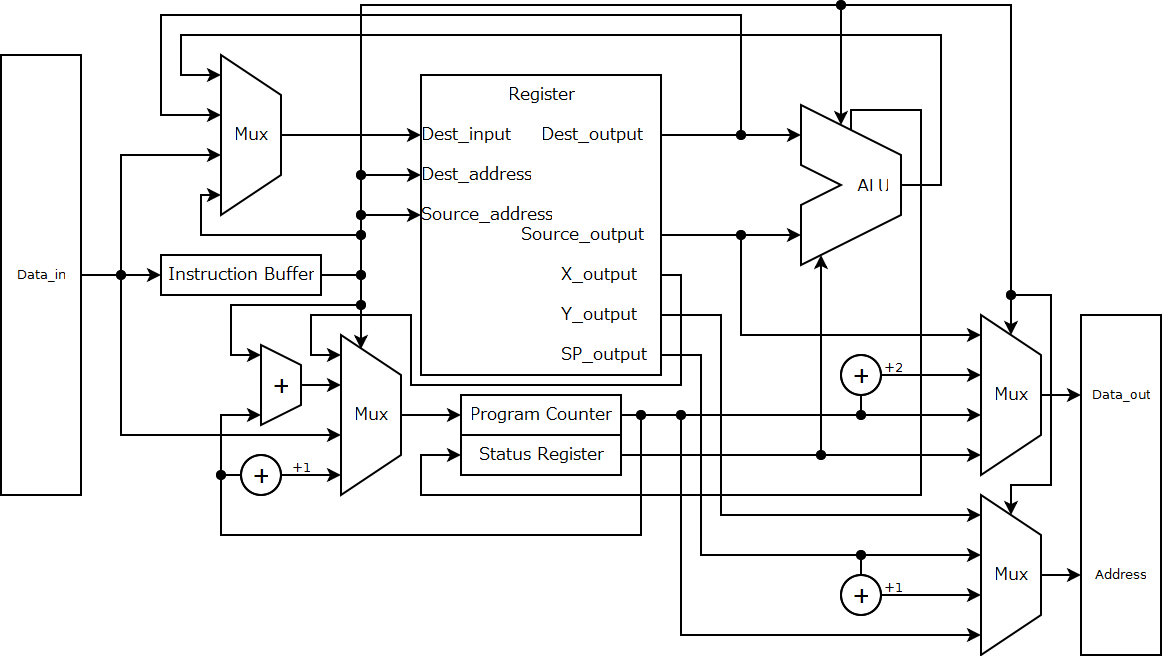

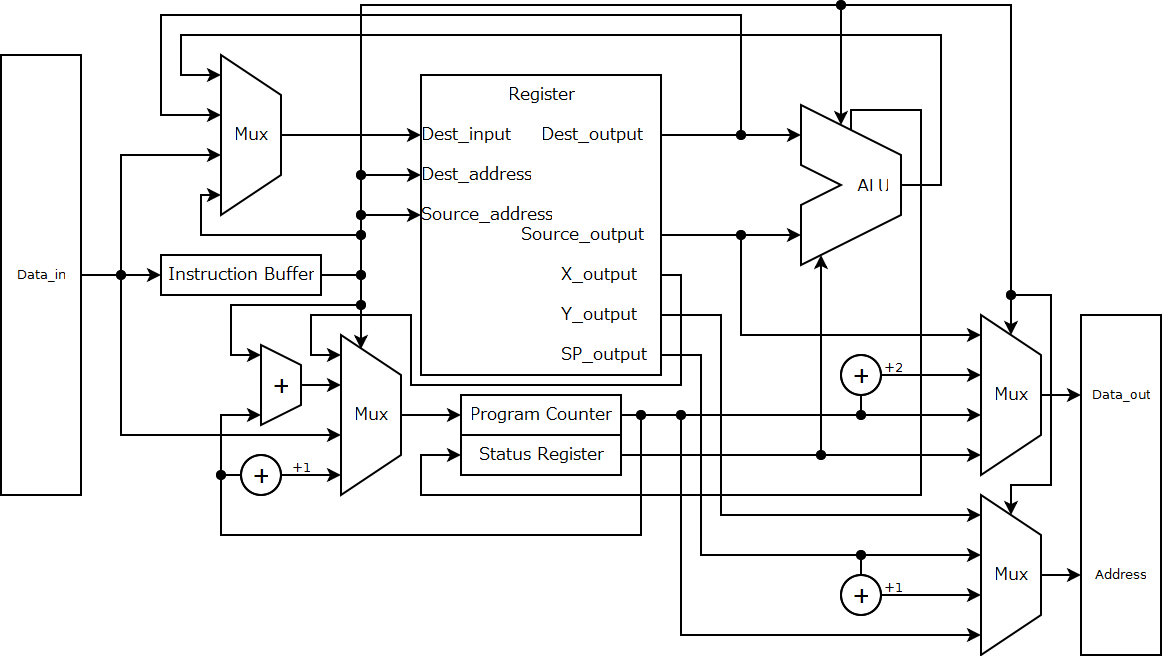

2-1.CPUのブロックダイアグラム

図1にブロックダイアグラムを示します。

図1 ブロックダイアグラム

図1の通り、汎用レジスタは2ポートあり、1ポートは読み出し専用のソース出力(Source_output)、

もう1ポートは読み書きに用いるディスティネーション入出力(Dest_input/Dest_output)になっています。

命令によってこの2ポートで入出力するレジスタが決定されます。つまり3オペランド形式は取ることができず、2オペランド形式に制限されます。

また、上記2ポートの他に、Xレジスタ(=R13)、Yレジスタ(=R14)、スタックポインタ(=R15)の出力があります。

これらの出力は一部の命令の実行に用いられます。

また、レジスタ-レジスタマシンであるため、ALUにおいて演算を行う命令の結果は必ずディスティネーションのレジスタに格納されます。

メモリ-レジスタ間のデータの転送はST,LD命令を用います。

2-2.汎用レジスタについて

このCPUは16bitの汎用レジスタを16本持ちます。どのレジスタも演算のソース/ディスティネーションになることができます。

しかし、一部のレジスタはさらに特殊な機能を持ちます。

- Xレジスタ(R13)は分岐系命令の分岐先指定に用いられます。

- Yレジスタ(R14)はメモリ-レジスタ間転送命令のメモリアドレス指定に用いられます。

- スタックポインタ(R15)はスタック操作関連の命令においてメモリアドレス指定に用いられます。

プログラムを書く場合、これらの制約を考慮する必要があります。

2-3.ステータスレジスタについて

ステータスレジスタは条件分岐や演算において使われるいくつかのフラグを格納するレジスタです。

詳細は「命令の一覧」をご覧下さい。

Copyright(C) 2010 R.Suzuki. All rights reserved.